# THC63LVD1023B / THC63LVD1024 Evaluation Kit

LVDS Dual Link Evaluation Board

Parts Number: THEVA1023B, THEVA1024

### 1. General Description

THEVA1023B and THEVA1024 are designed to evaluate THC63LVD1023B/THC63LVD1024 for transmission video data.

THC63LVD1023B and THC63LVD1024 chipset can transmit 67bit data via dual channel LVDS. The maximum input clock frequency of THC63LVD1023B is 160MHz, and the maximum output clock frequency of THC63LVD1024 is 135MHz at Dual in / Single out mode.

#### 2. Features

#### **Common Features**

- Low power single 3.3V CMOS design

- · Power down mode

- Wide dot clock range suited for TV signal(480i to 1080p), PC signal(VGA to QXGA)

- PLL requires no external components

- · Clock edge selectable

#### THC63LVD1023B

- Single/Dual TTL in, Single/Dual LVDS out

- Double Edge Input(Single in/Dual out Mode)

- Input Port Switch for Single TTL in/Dual out

- Asynchronous Dual TTL in / Dual LVDS out

- 3 LVDS Data Mapping Modes

- · Pseudo Random Pattern Generation Circuit

- · Support Reduced Swing LVDS for Lower EMI

- · LQFP 144 Pin

### THC63LVD1024

- · Single/Dual LVDS in, Single/Dual TTL out

- · Double Edge Output

- 50% Output Clock Duty Cycle

- TTL Clock Output Timing Programmable

- 2 Output Data Mapping Modes

- LQFP 144 pin + Exposed Pad

## 3. Overview

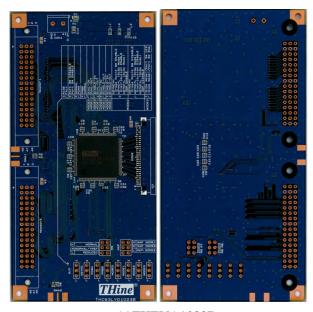

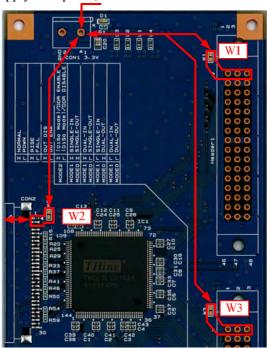

(a)THEVA1023B

(b)THEVA1024

Figure 1 THEVA1023B and THEVA1024

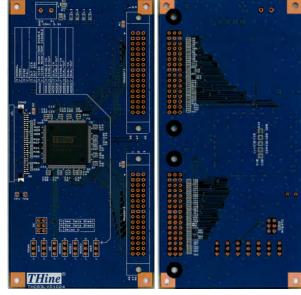

## 2. Power Supply Setup

This chapter shows power supply condition.

Caution: Please check if there is no power-GND short on below red trace before supplying any power.

### 3.3V Power Supply to Each Board

Each evaluation board requires 3.3V power supply. Please use "CON1" connector typically.

Figure 2 Power Supply for Evaluation Board

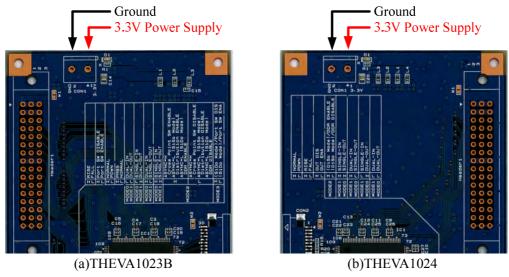

### Power Supply from / to Connector

3.3V power supply can be connected to Header1 and CON2 by using W1, W2 and W3solder jumper.

#### THEVA1023B

- W1: Connect the 3.3V power supply with pin#1, 2 and 3 of Header1.

- W2: Connect the 3.3V power supply with pin#13 and 14 of CON2.

- W3: Connect the 3.3V power supply with pin#1, 2 and 3 of Header2.

Figure 3 THEVA1023B Power Supply from / to Each Connector

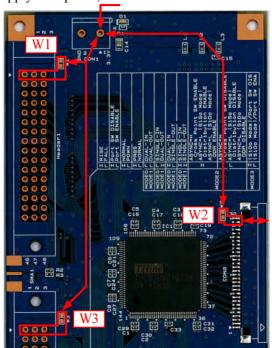

### **THEVA1024**

- W1: Connect the 3.3V power supply with pin#1, 2 and 3 of Header1.

- W2: Connect the 3.3V power supply with pin#1 and 2 of CON2.

- W3: Connect the 3.3V power supply with pin#1, 2 and 3 of Header2.

Figure 4 THEVA1024 Power Supply from / to Each Connector

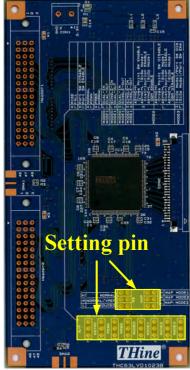

## 3. Function Setting

Setting pin of each board is shown in yellow area of Figure 5.

(b)THEVA1024

Figure 5 Position of Function Setting Pin

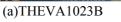

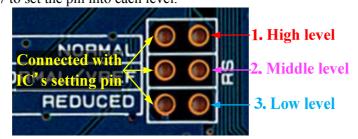

Pin#2 of each 3HEADER is connected to IC's setting pin.

Each setting pin's high or low setting can set by connecting pin#2 of 3HEADER and high level or low level.

Figure 6 High / Low Setting Description

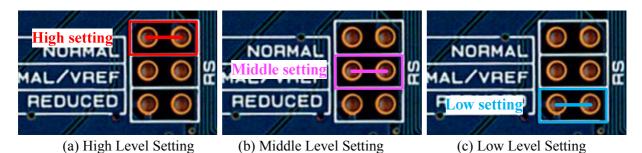

THEVA1023B and THEVA1024 have 3 level setting pin. Please refer to Figure 7 to set the pin into each level.

Figure 7 Description of 3Level Setting Pin

Figure 8 High / Middle / Low Setting Description

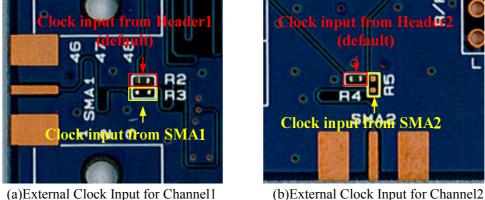

### 4. Clock Input from SMA Connector

THEVA1023B can also choose the TTL clock input from SMA connector by using 0ohm resistor. If you want to use SMA connector for clock input, please change the 0ohm resistor mount from R2 to R3, and R4 to R5.

Figure 9 TTL Clock Input Connector Select

Clock input

THine Electronics, Inc.

# **5. Status Indicate LED**

LED "D1" indicates 3.3V power supply status.

## 6. Function

This chapter shows function setting of THEVA1023B and THEVA1024.

Table 1 THEVA1023B Function Setting Description

| Silk   | Symbol | Function                                                                                                |                                                                                    |              |         |                   |           |                                    |             |                   |  |

|--------|--------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------|---------|-------------------|-----------|------------------------------------|-------------|-------------------|--|

|        |        | LVDS swing mode, VREF select.                                                                           |                                                                                    |              |         |                   |           |                                    |             |                   |  |

|        |        |                                                                                                         |                                                                                    | R            | RS LV   |                   | Swing     | Small Swing Input S                | upport      |                   |  |

| RS     | RS     |                                                                                                         |                                                                                    | $V_{\rm I}$  | НМ      | M 350m            |           | N / A                              |             |                   |  |

| I Co   |        |                                                                                                         |                                                                                    | $V_{\rm II}$ | MM      | <sub>4</sub> 350m |           | $RS = V_{REF}$                     |             |                   |  |

|        |        |                                                                                                         |                                                                                    | $V_{I}$      | LM      | 200n              | ıV        | N / A                              |             |                   |  |

|        |        | LV                                                                                                      | DS mapp                                                                            | ing table    | selec   | t                 |           | •                                  |             |                   |  |

|        |        |                                                                                                         | - ~FF                                                                              | 8            | ~~~~    | MA                | AP        | Mapping Mode                       |             |                   |  |

| MAP    | MAP    |                                                                                                         |                                                                                    |              | F       |                   | IM        | Mapping MODE1                      |             |                   |  |

|        |        |                                                                                                         |                                                                                    |              |         | V <sub>IM</sub>   | ſМ        | Mapping MODE2                      |             |                   |  |

|        |        |                                                                                                         |                                                                                    |              |         | $V_{IL}$          | .M        | Mapping MODE3                      |             |                   |  |

| MODE3  | MODE3  |                                                                                                         |                                                                                    |              |         |                   |           | nen $MODE[1:0] = H$                | L(Single-   | in / Dual-out).   |  |

| WIODLS | WODLS  |                                                                                                         | H or Open                                                                          | : Port Sw    | vitch 1 | Disable           | <u>L:</u> | Port Switch Enable                 |             |                   |  |

|        |        | Th                                                                                                      | e use of th                                                                        | ese multi    | i-func  | ction de          | pends     | s on the setting of M              | ODE[1:0]    | or ASYNC.         |  |

|        | MODE2  |                                                                                                         | ASYNC                                                                              | MODE1        | DE1 M   |                   |           | Function                           | MODE2       | Enable / Disable  |  |

|        |        |                                                                                                         |                                                                                    | MODE         | 171     | ODE0              |           | Cross Point                        | Н           | Enable Enable     |  |

| MODE2  |        |                                                                                                         | Н                                                                                  | X            | X       |                   |           | Switching                          | L           | Disable           |  |

|        |        |                                                                                                         | L                                                                                  | Н            |         | Н                 |           | Distribution                       | Н           | Enable            |  |

|        |        |                                                                                                         |                                                                                    |              |         |                   |           | Function                           | L           | Disable           |  |

|        |        |                                                                                                         | I                                                                                  |              |         | L                 | DDF       | R(Double Edge Input)<br>Function   | H<br>L      | Enable<br>Disable |  |

|        |        | Pix                                                                                                     | cel data mo                                                                        | ode selec    | t       |                   |           |                                    |             | <u> </u>          |  |

| MODE1  | MODE1  |                                                                                                         |                                                                                    |              | ODE1    | MOI               | DE0       | Function                           | 1           |                   |  |

|        |        |                                                                                                         |                                                                                    |              | L I     |                   |           | Dual Link (Dual-in / Dual -        |             | <del></del>       |  |

|        |        |                                                                                                         |                                                                                    |              | L       | H                 |           | Dual Link (Single-in               |             |                   |  |

| MODE0  | MODE0  | Į                                                                                                       |                                                                                    |              | H L     |                   | ,         | Single Link (Dual-in / Single-out) |             |                   |  |

|        |        | H H Single Link (Single-in / Single-out)                                                                |                                                                                    |              |         |                   |           |                                    |             | ut)               |  |

|        |        | As                                                                                                      | ynchronou                                                                          | ıs functio   | n.      |                   |           |                                    |             |                   |  |

| ASYNC  | ASYNC  | H: Asynchronous Function Enable (MODE[1:0] function is enabled in this setting)                         |                                                                                    |              |         |                   |           |                                    |             |                   |  |

|        |        |                                                                                                         | L : Asynchronous Function Disable (MODE[1:0] function is disabled in this setting) |              |         |                   |           |                                    |             |                   |  |

| R/F    | R/F    | Input clock triggering edge select.  H: Rising Edge L: Falling Edge                                     |                                                                                    |              |         |                   |           |                                    |             |                   |  |

|        |        | PRBS (Pseudo Random Binary Sequence) generator is active in order to evaluate eye                       |                                                                                    |              |         |                   |           |                                    |             |                   |  |

| PRBS   | PRBS   | diagram when MODE[1:0] = L, L (Dual-in / Dual-out) or A<br>H: PRBS Generator Enable L: Normal Operation |                                                                                    |              |         | SYNC = H          | I.        |                                    |             |                   |  |

|        |        | -                                                                                                       | H : PRBS<br>wer down                                                               |              |         |                   | . : No    | rmai Operation                     |             |                   |  |

| PDWN   | PDWN   |                                                                                                         |                                                                                    |              |         |                   | ver D     | own Mode (All outp                 | uts are Hi- | Z)                |  |

|        | I      | <u> </u>                                                                                                |                                                                                    |              |         |                   |           | \ I                                |             | *                 |  |

Table 2 THEVA1024 Function Setting Description

| Silk   | Symbol | Function                                   |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

|--------|--------|--------------------------------------------|---------------------------------------------------------------------------------|------|------------|---------|------------------------------------|-------------------------|------|--|--|--|

|        |        | LVDS swing mode, V <sub>REF</sub> select.  |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

|        |        |                                            | [                                                                               | MOD  | E1 N       | 4ODEA   | DIZ                                | E                       |      |  |  |  |

|        |        |                                            | •                                                                               | MOD  | EI N       | 1ODE0   | DK                                 | 1                       |      |  |  |  |

|        | DK     |                                            |                                                                                 |      | LL         |         | L                                  | 0                       |      |  |  |  |

| DK     |        |                                            |                                                                                 |      | H L<br>H H |         | M                                  | -6(tDOUT)/28            |      |  |  |  |

|        |        |                                            |                                                                                 |      | пп         |         | Н                                  | 6(tDOUT)/28             |      |  |  |  |

|        |        |                                            |                                                                                 |      |            |         | L                                  | 0                       |      |  |  |  |

|        |        |                                            |                                                                                 |      | LH         |         | M                                  | -7(tDOUT)/28            |      |  |  |  |

|        |        |                                            |                                                                                 |      |            |         | Н                                  | 7(tDOUT)/28             |      |  |  |  |

|        |        | DDR functi                                 | DDR function enable. The use of this function depends on the setting MODE[1:0]. |      |            |         |                                    |                         |      |  |  |  |

|        |        |                                            | MODE                                                                            | 1 M( | ODE0       | MODI    | E <b>2</b>                         | Function                |      |  |  |  |

|        | MODE2  |                                            | L                                                                               |      | L          | L       |                                    | Must be tied to G       | ND   |  |  |  |

| MODE2  |        |                                            | L                                                                               | Н    |            | Н       |                                    | DDR Function En         |      |  |  |  |

|        |        | -                                          |                                                                                 |      |            | L       |                                    | DDR Function Dis        |      |  |  |  |

|        |        | -                                          | H                                                                               | _    | L          | L       |                                    | Must be Tied to G       |      |  |  |  |

|        |        |                                            | Н                                                                               |      | Н          | L       |                                    | Must be Tied to G       | ND   |  |  |  |

|        | MODE1  | Pixel data mode select                     |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

| MODE1  |        |                                            | MODE1                                                                           |      | MODI       | Ε0      |                                    | Function                |      |  |  |  |

|        |        |                                            | I                                                                               |      | L          | D       | ual Li                             | nk (Dual-in / Dual -ou  | ıt)  |  |  |  |

|        |        |                                            | I                                                                               |      | Н          | Du      | ıal Lin                            | nk (Single-in / Dual -o | ut)  |  |  |  |

| MODE0  | MODE0  |                                            | Н                                                                               |      |            |         | Single Link (Dual-in / Single-out) |                         |      |  |  |  |

|        |        |                                            | I                                                                               | I    | Н          | Sing    | gle Lir                            | nk (Single-in / Single- | out) |  |  |  |

| OE     | OE     | Output enable                              |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

| OL     | OL     | H : Output Enable L : Output Disable       |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

| D/E    | R/F    | Output clock triggering edge select.       |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

| R/F    |        | H : Rising Edge<br>L : Falling Edge        |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

|        |        | Power down function setting                |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

| PDWN   | PDWN   | H: Normal Operation                        |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

|        |        | L : Power Down Mode (All outputs are Hi-Z) |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

| MAP    | MAP    | LVDS map                                   |                                                                                 |      |            |         |                                    |                         |      |  |  |  |

| 171771 | 171771 | H : Mapp                                   | oing MO                                                                         | DE1  | L: M       | lapping | MOD                                | DE2                     |      |  |  |  |

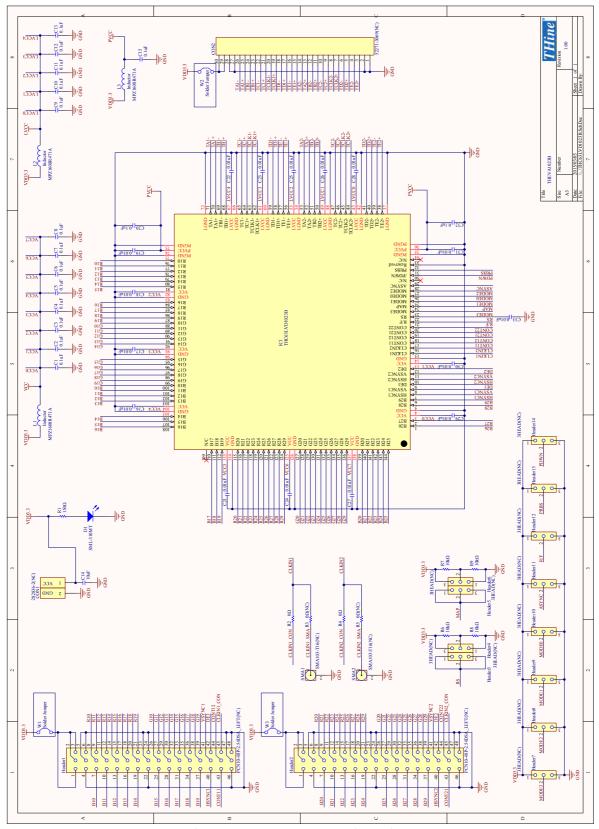

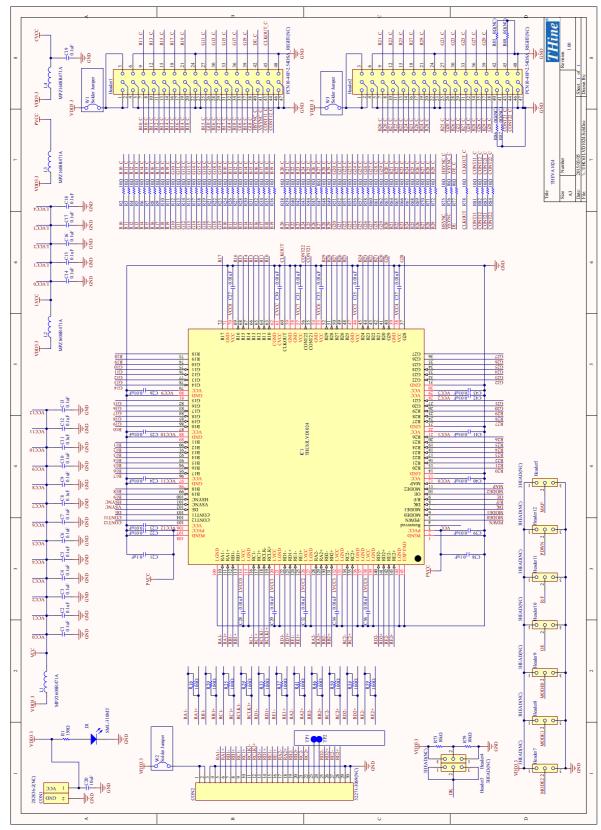

## 7. Schematic

Figure 10 THEVA1023B Schematic

Figure 11 THEVA1024 Schematic

# **8. Bills of Materials**

### Table 3 THEVA1023B BOM

| TYPE      | Value / Part No.           | Package      | SPEC         | Reference No.                                                                                                      | Q'ty | Note |

|-----------|----------------------------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------|------|------|

| Capacitor | 0.1uF                      | 1005         | 16V          | C1, C2, C3, C4, C5, C6, C7, C8, C9, C10, C11, C12, C13, C15, C20, C32                                              | 17   |      |

| Capacitor | 10uF                       | 2012         | 16V          | C14                                                                                                                | 1    |      |

| Capacitor | 0.01uF                     | 1005         | 16V          | C16, C17, C18, C19, C21, C22, C23, C24, C25, C26, C27, C28, C29, C30, C31, C33                                     | 16   |      |

| Connector | 282836-2(NC)               | 5mm_pitch    | 2pin         | CON1                                                                                                               | 1    |      |

| Connector | 52271-3069(NC)             | 1mm_pitch    | 30pin        | CON2                                                                                                               | 1    |      |

| Connector | PCN10-48P-2.54DSA_LEFT(NC) | 2.54mm_pitch | 48pin        | Header1, Header2                                                                                                   | 2    |      |

| Connector | SMA103-T16(NC)             | 1.6mm        | PCB End Jack | SMA1, SMA2                                                                                                         | 2    |      |

| Header    | 3HEAD(NC)                  | 2.54mm_pitch |              | Header3, Header4, Header5, Header6, Header7, Header8,<br>Header9, Header10, Header11, Header12, Header13, Header14 | 12   |      |

| IC        | THC63LVD1023B              | LQFP144      |              | IC1                                                                                                                | 1    |      |

| Inductor  | MPZ1608R471A               | 1608         | 1.2A         | L1, L2, L3                                                                                                         | 3    |      |

| LED0      | SML-310MT                  | 1608         | GREEN        | D1                                                                                                                 | 1    |      |

| Resistor  | 150Ω                       | 1005         | 0.1W         | R1                                                                                                                 | 1    |      |

| Resistor  | $0\Omega$                  | 1005         | 0.1W         | R2, R4                                                                                                             | 2    |      |

| Resistor  | $0\Omega(NC)$              | 1005         | 0.1W         | R3, R5                                                                                                             |      |      |

| Resistor  | 10kΩ                       | 1005         | 0.1W         | R6, R7, R8, R9                                                                                                     | 4    |      |

### Table 4 THEVA1024 BOM

| TYPE      | Value / Part No.            | Package      | SPEC  | Reference No.                                                 |    | Note |

|-----------|-----------------------------|--------------|-------|---------------------------------------------------------------|----|------|

| Capacitor | 0.1uF                       | 1005         | 16V   | C1, C2, C3, C4, C5, C6, C7, C8, C9, C10, C11, C12, C13, C14,  |    |      |

| Capacitor | 10uF                        | 2012         | 16V   | C20                                                           |    |      |

| Consoitor | 0.01uF                      | 1005         | 16V   | C22, C23, C24, C25, C26, C27, C28, C29, C30, C31, C32, C33,   | 21 |      |

| Capacitor | 0.01ur                      |              |       | C34, C35, C36, C37, C39, C40, C41, C42, C43                   | 21 |      |

| Connector | 282836-2(NC)                | 5mm_pitch    | 2pin  | CON1                                                          | 1  |      |

| Connector | 52271-3069(NC)              | 1mm_pitch    | 30pin | CON2                                                          | 1  |      |

| Connector | PCN10-48P-2.54DSA_RIGHT(NC) | 2.54mm_pitch | 48pin | Header1, Header2                                              |    |      |

| Header    | 3HEAD(NC)                   | 2.54mm_pitch |       | Header3, Header4, Header5, Header6, Header7, Header8,         |    |      |

| IC        | THC63LVD1024                | LQFP144      |       | IC1                                                           | 1  |      |

| Inductor  | MPZ1608R471A                | 1608         | 1.2A  | L1, L2, L3, L4                                                | 4  |      |

| LED0      | SML-310MT                   | 1608         | GREEN | D1                                                            | 1  |      |

| Resistor  | 150Ω                        | 1005         | 0.1W  | R1                                                            | 1  |      |

|           |                             |              |       | R2, R3, R4, R5, R6, R7, R8, R9, R10, R11, R12, R13, R14, R15, |    |      |

| Dagistan  | $10\Omega$                  | 1005         | 0.1W  | R17, R18, R19, R21, R22, R23, R24, R26, R27, R28, R30, R31,   | 68 |      |

| Resistor  |                             |              |       | R32, R34, R35, R36, R38, R39, R40, R42, R43, R44, R45, R47,   | 08 |      |

|           |                             |              |       | R48, R49, R51, R52, R53, R55, R56, R57, R58, R60, R61, R62,   |    |      |

| Resistor  | $100\Omega$                 | 1005         | 0.1W  | R16, R20, R25, R29, R33, R37, R41, R46, R50, R54, R59         | 11 |      |

| Resistor  | 10kΩ                        | 1005         | 0.1W  | R73, R74, R79, R80                                            | 4  |      |

| Resistor  | 0Ω(NC)                      | 1005         | 1A    | R85, R86, R87, R88                                            | 4  |      |

# 9. Set Items

Table 5 Set Items

| ТҮРЕ                              | Part No.   |

|-----------------------------------|------------|

| DC Connector                      | 282836-2   |

| FFC Connector for LVDS Link       | 52271-3069 |

| FFC 30pin 1mm Pitch for LVDS Link | 98267-0475 |

| Pin Header                        |            |

It's possible to mount these parts on this board and use.

### 10. Notices and Requests

Please kindly read, understand and accept this "Notices and Requests" before using this product.

#### For the Material:

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to design of respective customers. Thine Electronics, Inc. ("Thine") is not responsible for possible errors and omissions in this material. Please note if the errors or omissions should be found in this material, Thine may not be able to correct them immediately.

- 3. This material contains THine's copyright, know-how or other proprietary. Copying or disclosing of the contents of this material to any third party without THine's prior permission is strictly prohibited.

### For the Product:

- 1. This product is solely designed for evaluation purpose, and other purposes including mass production and distribution are not intended.

- 2. This product has been solely manufactured for electric design engineers but not for end-users.

- 3. This product is not radiation-tolerant product.

- 4. This product is presumed to be used for general electric device, not for applications which require extremely high-reliability/safety (including medical device concerned with critical care, aerospace device, or nuclear power control device). Also, when using this product for any device concerned with control and/or safety of transportation mean, traffic signal device, or other various types of safety device, such use must be after applying appropriate measures to the product.

- 5. This product has been designed with the utmost care to accomplish the purpose of evaluation of IC products manufactured by THine Electronics, Inc., however, THine MAKES NO WARRANTIES OR REPRESENTATIONS WITH REGARD TO ANY PERFORMANCE OR FUNCTION OF THIS PRODUCT IN ANY CIRCUMSTANCE.

- 6. This product has been manufactured with the utmost care in quality control and product reliability, however, there may be faults or defects with a low but fixed probability, as inevitable phenomenon concerned with semiconductor manufacturing processes. Therefore, Customers are encouraged to have sufficiently redundant or error-preventive design applied to the use of the product so as not to have THine's product cause any social or public damage. Replacement of the product is only available in case of obvious defects of mount devices at the point of unpacking the product. Neither replacement nor failure analysis of the product is available in any other case of defects with the product and/or the product's components.

- 7. Customers are asked, if required, to judge by themselves on whether this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Control Law.

- 8. Please Note that if infringement of any third party's industrial ownership should occur by using this product, THine will be exempted from any responsibility unless it directly relates to the production process or functions of the product.

- 9. Developing, designing and manufacturing of Customers' own products, equipments or system by using of this product is strictly prohibited in any way.

## THine Electronics, Inc.

sales@thine.co.jp